Intel has always relied on the famous, established architecture – Ring Bus – for intra-processor communication. Efficient data movement across all components has a tremendous impact on performance. To achieve efficient intra-chip communication, Intel had introduced the Ring Bus architecture. Intel’s ring bus connects various components with a bi-directional bus. The Ring Bus moved through the most important parts inside the processor, including cores, integrated memory controllers, PCI Express, I/O controllers, caches etc. But then, Ring Bus has its own set of limitations – particularly it doesn’t scale well when the number of cores starts becoming massive. To overcome the limitations of the Ring Bus, Intel is now introducing a brand new architecture for intra-processor communication.

Intel Xeon and Skylake-X to come with mesh architecture

When it comes to addressing the needs of the data center, Intel is keen on taking its current architecture to the next level. One of the important factors in data center architecture design is the emphasis on greater efficiency to get the best return on capital and maximize output within footprint and power constraints. Some of the challenges being faced with the increasing number of cores –

- Increasing bandwidth between cores, on-chip cache hierarchy, memory controller and I/O controllers.

- Reducing latency when accessing data from on-chip cache, main memory or other cores.

- Creating energy efficient ways to supply data to cores and I/O from on-chip cache and memory.

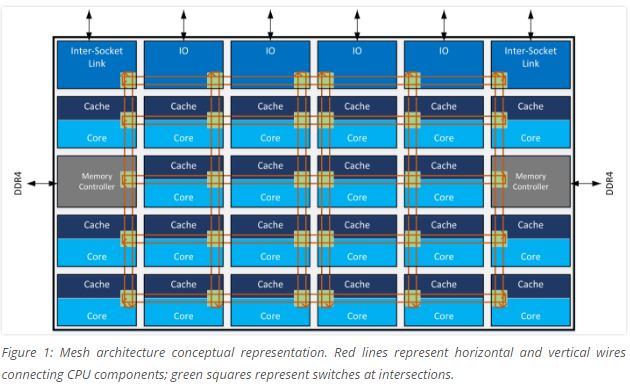

Intel has now introduced an innovative “mesh” on-chip interconnect topology as part of Intel Xeon Scalable processors. The new topology delivers low latency and high bandwidth among cores, memory and I/O controllers.

“By providing a more direct path than the prior ring architectures and many more pathways to eliminate bottlenecks, the mesh can operate at a lower frequency and voltage and can still deliver very high bandwidth and low latency. This results in improved performance and greater energy efficiency similar to a well-designed highway system that lets traffic flow at the optimal speed without congestion”, says Intel’s Akhilesh Kumar in his blog post.

Intel’s Xeon and the Skylake-X processors are expected to come with the new mesh interconnect topology. The innovative architecture will enable performance and efficiency improvements across the broadest variety of usage scenarios.